TWiki> P1076/Ballots Web>CollectedRequirements>P1076BallotsInterfaceAndBundleEnhancements>UCInterfaceDocRTLBundles (2016-11-15, BrentHahoe)EditAttach

P1076/Ballots Web>CollectedRequirements>P1076BallotsInterfaceAndBundleEnhancements>UCInterfaceDocRTLBundles (2016-11-15, BrentHahoe)EditAttach

3.2. RTL Design

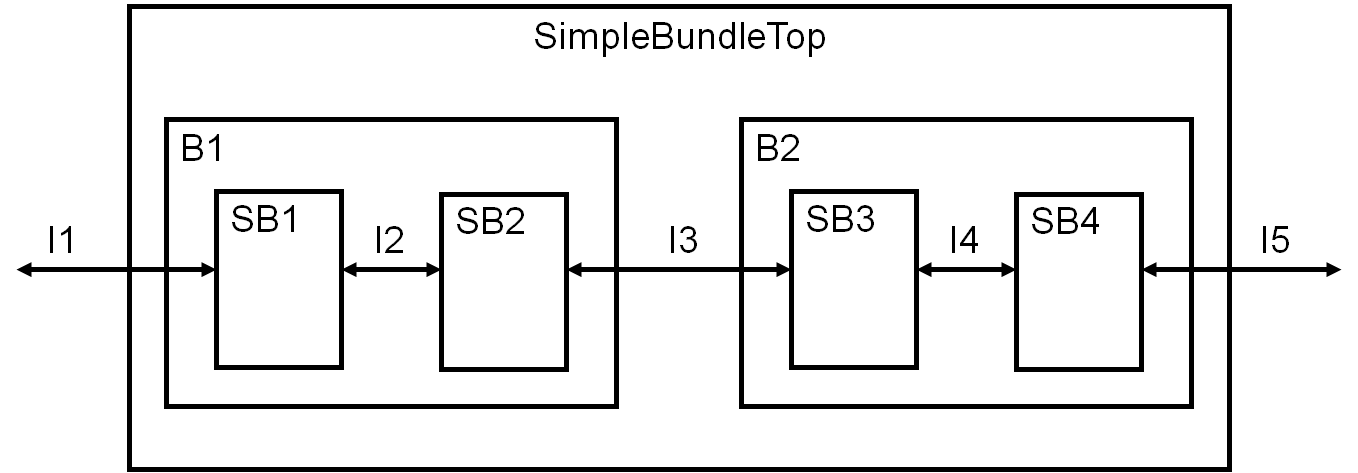

3.2.1. Simple Bundles

Connectivity of RTL functions consists of one or more signal objects. A bundle is a simplified form of an interface that allows this connectivity to be referenced as a single object. As such it is a composite similar in some ways to a record. One difference is that since a bundle is a port, there must be a method to resolve the IO direction of each element. Different elements may have a different IO direction. A simple model for connectivity using bundles is shown below. SimpleBundleTop is the top level of the design. B1 and B2 are subblocks of SimpleBundleTop. SB1 and SB2 are subblocks of B1. SB3 and SB4 are subblocks of B2. Each connection (labled I1, I2, I3, I4, and I5) is a bundle. Within a bundle at any subblock, a given element may be mode in, out, or inout. Bundle elements typically have

different IO modes at opposite ends of the interface. An element of bundle I2 that is mode “in” at SB1 will be mode

“out” at SB2. Bundle elements typically have same IO modes as the bundle is propagated up or down through the

hierarchy. An element of bundle I3 that is mode “in” at SB2 will be mode “in” at B1.

Within a bundle at any subblock, a given element may be mode in, out, or inout. Bundle elements typically have

different IO modes at opposite ends of the interface. An element of bundle I2 that is mode “in” at SB1 will be mode

“out” at SB2. Bundle elements typically have same IO modes as the bundle is propagated up or down through the

hierarchy. An element of bundle I3 that is mode “in” at SB2 will be mode “in” at B1.

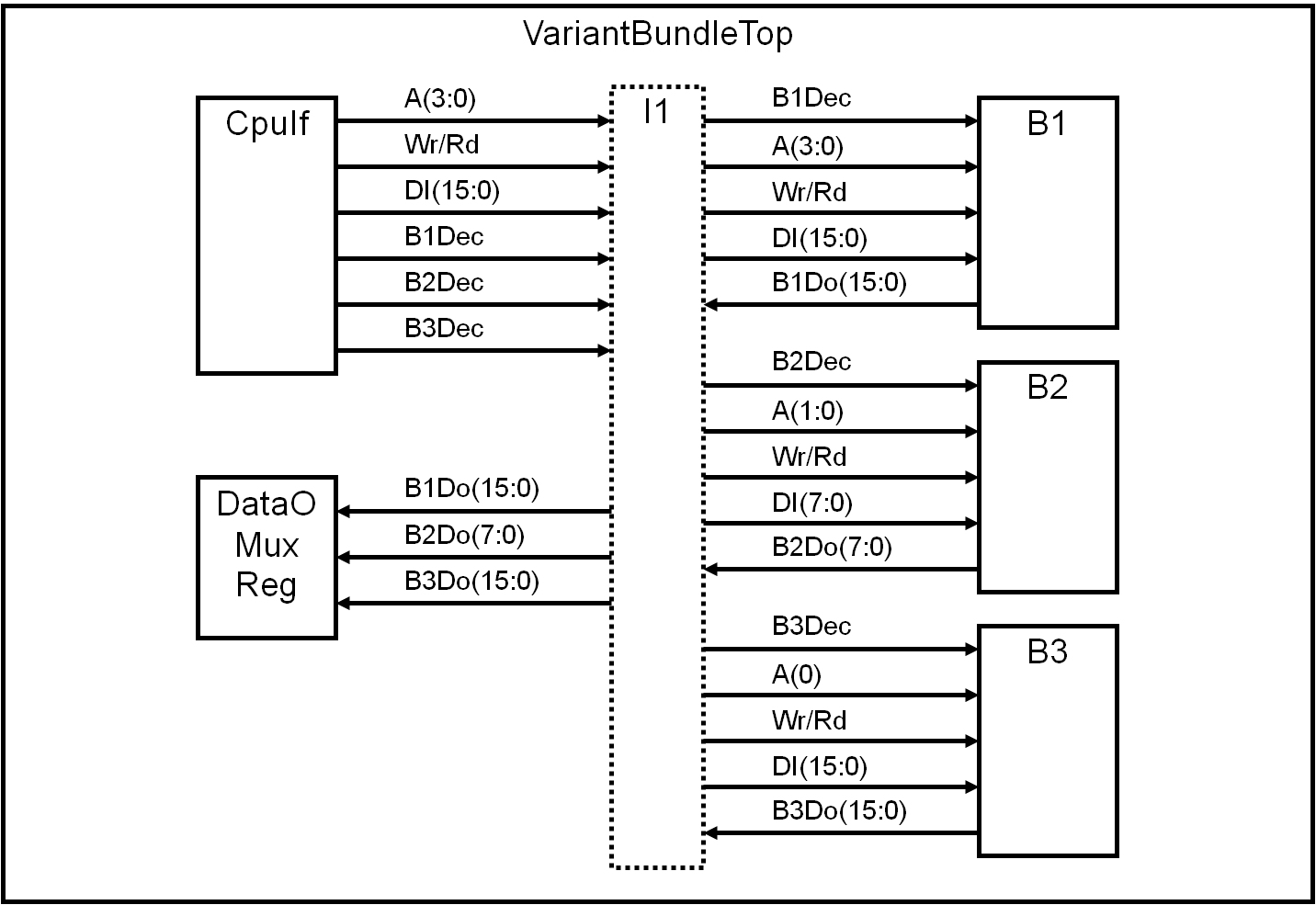

3.2.2. Variant Bundles

The simple view of bundles is that every block connects to every element of the bundle. This is not always the case. The following example shows potential connectivity of addressable logic. Note that in this case a subblock does not either drive or read some elements of the interface. In fact some subblocks do not use all bits of some array elements (note A and DI at B1, B2, and B3). From a synthesis standpoint, having unused elements on a composite is problematic - they show up as unconnected ports to backend tools. As a result, a method to specify partial connectivity to a bundle is desirable.

| I | Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

IFDocRTLSimpleBundleTop.png | manage | 14.6 K | 2015-07-21 - 14:45 | BrentHahoe | |

| |

IFDocRTLVariantBundles.png | manage | 43.0 K | 2015-07-21 - 14:50 | BrentHahoe |

Topic revision: r5 - 2016-11-15 - 18:23:41 - BrentHahoe

Copyright © 2008-2026 by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Ideas, requests, problems regarding TWiki? Send feedback

Ideas, requests, problems regarding TWiki? Send feedback